|

||

Home > TERATEC FORUM > Workshops

Workshops - Wednesday October 14

Workshop 2 - 16:00 to 17:30

Do you speak Exascale?

Chaired by Guillaume Colin de Verdière, Senior Expert on HPC and Jean-Philippe Nominé, HPC Strategic Collaborations Manager, CEA DAM

Redefining “Exascale”: The Third Great Disruption of HPC

In the 1970s, the introduction of vector processing disrupted supercomputing and caused the restructuring of scientific applications to achieve order-of-magnitude performance and efficiency gains over purely scalar CPUs.

Similarly, massively parallel processors in the 1990s displaced custom vector supercomputers, providing a similar ~10x performance and price/performance advantage over their predecessors, but at the cost of another restructuring of applications and algorithms to distribute work and data over 100s-1000s of relatively weak (and weakly-connected) commodity microprocessor-based nodes.

|

|

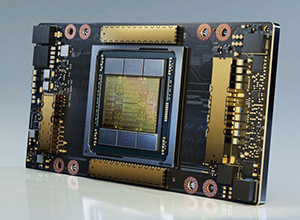

Today, in the growing vacuum created by Moore’s Law’s fade, we are a dozen years into the age of GPU-accelerated HPC computing. Like each preceding wave of disruption, GPU acceleration demands an investment be made in the application to achieve ~10x (or more) performance and efficiency boost.

The economical and ubiquitous power of GPUs also made possible the current explosion in AI, and the influence of AI on GPU architecture is exposing additional ~10x or larger potential gains for scientific computing as a result of new tensor functional units, reduced-precision data formats, and data-driven learned models. As a result, there are already multiple “AI supercomputers” with multi-EFLOPS (AI FLOPS) peaks in existence, and examples of scientific applications employing learned models capable of >EFLOPS effective performance on such systems, threatening the continued validity and usefulness of the traditional measurement of HPC systems using DP FLOPS in the very near future.

This talk will examine the set of AI-driven capabilities in the latest generation of data center GPUs, and explore their direct applicability to scientific numeric algorithms as well as the truly disruptive power of learned models to replace or augment numeric algorithms, and contemplate the question of whether anyone should continue to “speak Exascale” in the traditional DP sense in the future of supercomputing.

|

Biography : Steve Oberlin’s large-scale computing technology career has spanned nearly 40 years, launched in 1980 at Cray Research bringing up CRAY-1 supercomputer systems. Starting in 1981, he worked for Seymour Cray as a logic designer and project engineer on the CRAY-2 and CRAY-3 supercomputers. In 1988, he led early massively parallel processing research at Cray that ultimately led to his role as the chief architect of the CRAY T3D MPP and its successor, the CRAY T3E. He holds 15 architecture and design patents for the T3D and T3E.

Steve was VP of Hardware Engineering in Chippewa Falls, Wisconsin, for Cray/SGI from 1996 until early 1999, responsible for hardware development and support of all Cray products and their follow-ons. Steve left SGI to found Unlimited Scale, Inc., in July of 2000, and spent the next 13 years creating new cloud computing infrastructure management and intelligent resource optimization technologies for USI, Cassatt, and CA Technologies. Steve returned to HPC at NVIDIA in November 2013. As CTO for Accelerated Computing, he is responsible NVIDIA’s Tesla HPC data center products roadmap and architecture. A champion of GPU scaling and efficiency, over the past 5 years he has been evangelizing the potential and exploring the implications of AI models, workflows, frameworks, and hardware optimizations applied to traditional HPC problems and algorithms. |

|---|

Register now and get your badge here

- TERATEC Forum is strictly reserved for professionals.

- Participation to exhibition, conferences and workshops is free (subject to seats available)

- On line registration is obligatory.