|

||

Home > TERATEC FORUM > Workshops

Workshops - Wednesday October 14

Workshop 2 - 16:00 to 17:30

Do you speak Exascale?

Chaired by Guillaume Colin de Verdière, Senior Expert on HPC and Jean-Philippe Nominé, HPC Strategic Collaborations Manager, CEA DAM

The JSC modular approach to extreme scale computing

|

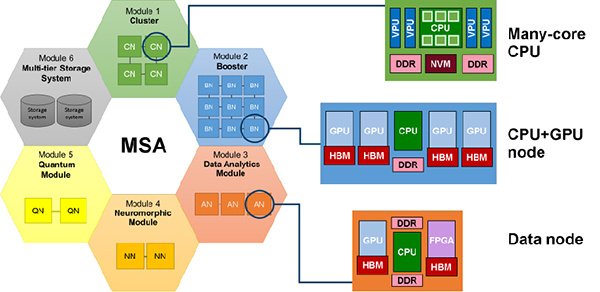

Reaching Exascale compute performances at an affordable monetary and energy cost calls for increasingly heterogeneous HPC systems, which combine general purpose processing units (CPUs) with acceleration devices (e.g. graphic cards (GPUs) or many-core processors) and even disruptive technologies (e.g. neuromorphic or quantum devices). The Modular Supercomputing Architecture developed within the EU-funded DEEP project series orchestrates all these resources at system-level, organizing them in compute modules. The goal is to provide cost-effective computing at extreme performance scale fitting the needs of a wide range of Computational Sciences.

In a modular supercomputer each application can dynamically decide which kinds and how many nodes to use, mapping its intrinsic requirements and concurrency patterns onto the hardware. Codes that perform multi-physics or multi-scale simulations can run across compute modules thanks to a global system-software and programming environment. Application workflows that execute different actions after (or in parallel) to each other can also be distributed in order to run each workflow-component on the best suited hardware, and exchange data either directly (via message-passing communication) or via the file-system.

This talk will describe the Modular Supercomputing Architecture – which constitutes the central element in the JSC’s roadmap to Exascale –, including its history, its hardware and software elements, and its current and upcoming implementations.

|

|

Biography : Dr. Estela Suarez is Senior Scientist and deputy-lead of the Technology Department at the Jülich Supercomputing Centre, which she joined in 2010. Her research focuses on HPC system architectures and co-design. As leader of the DEEP series of EU-funded projects she has driven the development of the Cluster-Booster and the Modular Supercomputing Architectures, including hardware, software and application implementation and validation. Additionally, since 2018 she leads the co-design efforts within the European Processor Initiative. Since 2018 she gives lectures on HPC architectures at the University of Bonn. She holds a PhD in Physics from the University of Geneva and a Master degree in Astrophysics from the University Complutense of Madrid. |

|---|

Register now and get your badge here

- TERATEC Forum is strictly reserved for professionals.

- Participation to exhibition, conferences and workshops is free (subject to seats available)

- On line registration is obligatory.